# An Innovative Approach of High Performance CMOS Based Current Conveyor-II for ASP Applications

## Ayushi Chaurasia, Rajinder Tiwari

Abstract— The main purpose of the paper is to present a CMOS current conveyor circuit which is best suited for the implementation of low- voltage, low-power and high bandwidth circuits. To achieve the bandwidth of current transfer function the circuit can be operated for a power supply of fraction of volt which is of MHz range and a power consumption of milli-watt range. Firstly, a class A current conveyor circuit operating from a single supply of fraction of volt having a high voltage swing capability is discussed and then the same circuit is modified to work as a class AB with a low voltage power supply in the fraction of volt range, while maintaining the same voltage swing capability. The body effect causes the threshold voltage variation and the current circuit realization is insensitive to it, which minimizes the layout area and makes both the circuits a valuable addition to the analog signal processing applications. The proposed structure has the required performance in terms of a bandwidth with level 3 CMOS technology and it operates as a linear circuit which is established with the help of 0.3 µm simulation using the PSpice software. In the field of analog signal processing this proposed current conveyor circuit has many applications. At 0.2µm the proposed circuit operates satisfactorily with high performance with the desired applications. The desired properties and the performance of the proposed circuit are confirmed by the PSpice simulation with the modeled parameters.

*Index Terms*— Current Conveyor (CC II), Analog Signal Processing, PSpice simulation, low votlage, high bandwidth, high performance, Current Mirror (CM), Operational Amplifiers (OA).

#### I. INTRODUCTION

In the analog circuit designing the current conveyors and unity gain amplifiers are widely used, especially in the signal processing applications [1-4]. The current controlled current source having unity gain amplification capability can be considered as the current conveyors (CC II). The circuit can be used in the realization of various sub-modules of the mixed analog processing applications of the systems [4, 5] and can also be used to take out the current flowing through a floating branch of a circuit. To obtain good dynamic swing at the output and high output so as to achieve a good cascadability, the high performance current mirror circuits are utilized in the CC-II. Most of the current conveyor circuits require high bias voltages as reported in the research sections of the various literatures. Thus, there always exists the requirement of the discussion of the CC circuits that can operate at low voltages and low currents. CC-I, CC-II and CC-III are the

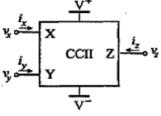

categorization of the basic current conveyor circuit [6, 8]. In the practical application of the analog signal processing, the CC-II has been proved to be more versatile as compared to the earlier one. The properties of the port of CC-II can be discussed as given below:

Fig. 1: Basic symbol of CC-II

Fig. 2: Block approach of CC-II

$$V_x = V_y$$

,  $I_y = 0$ ,  $I_z = \pm I_x$  ... Basic Equations (1)

| lv ] | ĨO | 0 | 0TVv]                | CCII Node | Impedance level  |

|------|----|---|----------------------|-----------|------------------|

| 14   | i. |   | 0 Vy<br>0 Ix<br>0 Vz | X         | Low (ideally 0)  |

| VX = | 4  | U | U IX                 | Y         | High (ideally a) |

| lz   | 0  | 1 | 0 Vz                 | 2         | High (ideally ∞) |

Fig. 3: Performance Characteristics of CC-II

The matrix given above explains the port properties of a basic current conveyor structure, where Ix, Iy and Iz are the currents flowing in X, Y and Z nodes respectively. And Vx, Vy and Vz are the respective voltages in these nodes. Comparing it to CC-I, the innovation of this circuit can be represented by the absence of the current parameter in Y node, which owes to the high impedance. The signal applied to the Y node is almost equal to the X node and is given as:

$$\alpha = \frac{Vx}{g_m r_o R_{XLOAD}}$$

(2)

$$\beta = \frac{l_z}{l_x} = 1 \tag{3}$$

Similarly, the ratio of the current Ix and Iz is discussed with the help of the equation (3). The following equations determine the various dominant parameters of a CC-II circuit.

Ayushi Chaurasia, Department of Electrical and Electronics, Amity University Lucknow

Rajinder Tiwari, Department of Electrical and Electronics, Amity University Lucknow

$$V_{in} = \sqrt{\frac{2I_{in}}{\beta_1}} + \Delta V_{th} + |V'|$$

(4)

$$R_{in} \approx \frac{1}{g_m}$$

(5)

$$R_{out} \approx \frac{g_m g_{m2}}{q_d q_{d2}} \tag{6}$$

$$Z_y = \gamma W L C_{ox} \tag{7}$$

Where  $\beta$ ,  $g_m$ ,  $g_d$ ,  $g_{m2}$  and  $g_{d2}$  are the dominant parameters that are used to discuss the performance of the CC-II circuit. And V' parameter is given by equation (8).

$$V' = nV_t \ln \left\{ \frac{L_4 \ I_{bias1}}{W_4 \ I_{DD4}} \right\} \tag{8}$$

#### II. THE BASIC CURRENT CONVEYOR CIRCUIT:

In the development of the analog and mixed signal processing applications the current conveyor circuits plays an important role using the CMOS approach [9, 13]. The CC-II is a three element device, which is basically defined with the help of three basic equations given.

$$Z_{y} = \gamma W L C_{ox}$$

<sup>(9)</sup>

$$Z_x \cong \frac{r_0 + R_{ZLOAD}}{1 + g_m r_0} \cong \frac{1}{g_m}, \text{ if } r_0 >> R_{ZLOAD}$$

(10)

$$Z_z = r_0 + (1 + g_m r_o) R_{XLOAD}$$

(11)

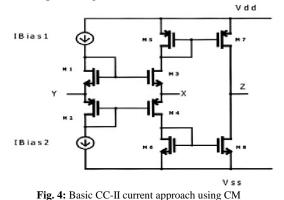

In the design of analog signal processing circuits the CC-II act as the natural building block in the research field. It is observed that the signal applied to the y node (MOS gate) is almost equal to the signal obtained at the X node (source of the MOS). The ratio is approximately equal to 1 between the currents  $I_x$  and  $I_z$  and a constant parameter  $\beta$  determines it. The impedance behavior of the circuit at Y node can be determined as the gate capacitance of the MOS which is quite high as per the required parameters. Practically,  $\gamma$  being a constant parameter whose theoretical value becomes 2/3 in the saturation region, otherwise it is 1, W(width) and L(length) of the MOS transistor respectively, Cox is the unitary gain capacitance, and these can be related in the following manner i.e. [14]. From the fig. 4 CC-II circuit it is assumed that the two biasing currents are required to be equal. Also, that the product g<sub>m</sub>r<sub>o</sub> value is much greater than unity and then the voltage characteristic of the circuit can be represented as:

$$\alpha = \frac{v_x}{v_y} = \frac{1}{1 + \frac{1}{(g_{m3} + g_{m4})(\frac{r_{03}}{r_{04}})}} \cong 1$$

(12)

With respect to the traditional implementations which utilize the commercial integrated circuits as the voltage OAs, CC-II based solution is used which reduces the system complexity. Many presentations and articles have witnessed the evolution of the first CC concept, demonstrating the universality of the element in the synthesis of almost all the active functions. To enhance the performance and the utility of the CCII block its evolution has regarded internal topology by maintaining the matrix characteristics. Firstly the CC-II was realized in bipolar technology as commercial products [14, 16]. The advent of MOS transistors has pushed the most of actual integrated solutions towards the use of CMOS technology having higher design simplicity and low power consumption particularly in low voltage portable system applications. CMOS devices suffers from many problems such as body effect, threshold voltage mismatch between nMOS pMOS and lower  $g_m$  values but its low cost especially for a standard technology represents a decisive feature towards its success and utilization. In the implementation of analog basic function the CC is widespread used. CCII-based circuits are always simpler in structure and more versatile, basically for the circuits which has high impedance current output capabilities with respect to commercial solutions with OAs [17, 18]. Furthermore, with the use of CCIIs, the heavy OA limitation of the constant gain-bandwidth product is definitely overcome.

#### III. PROPOSED CURRENT CONVEYOR CIRCUIT:

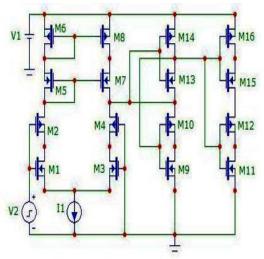

By using basic CC-IIs we can implement a number of analog applications such as voltage and current amplifiers, current differentiators and integrators, capacitance multipliers, impedance simulators and converters, bi-quadratic filters [19, 26]. voltage-to-current and current-to-voltage converters, instrumentation amplifiers, oscillators and waveform generators, etc.. Many solutions are given in the literatures that were used in the past but now new possibilities along with high performance can be certainly considered for the future, especially at lower supply voltages and with more reduced dissipation. The implementation of the basic current conveyor holds an important aspect, having the operation and behavior of its non-ideal characteristics i.e. input and output real and imaginary parasitic impedances, current and voltage transfer functions. This approach leads us in the direction of an enhanced and modified model for the CC-II device [27, 29]. Moreover, the development of novel architectures able to implement analog functions with a lower number of basic elements can be of certain interest for the researchers with new fields of applications for the CC-II, i.e. the development of current-mode sensor interface circuits. The proposed circuit has four current mirrors, one biasing resistor and a translinear section which is composed of two current quasi-mirrors which are topologically similar to the current mirrors but they behave differently. The type of current mirror to be used depends on the application for which the circuit is designed and for which output voltages are needed in excess of the threshold voltage to operate properly. The basic current conveyor with simple current mirrors is implemented with a smaller number of transistors, influences the bandwidth of the circuit, i.e. it allows operation at higher frequencies. A smaller power supply voltage is needed for biasing of smaller no. of transistors and the power consumption is reduced. If all the CMOS transistors have matched characteristics and

## International Journal of Engineering and Applied Sciences (IJEAS) ISSN: 2394-3661, Volume-4, Issue-5, May 2017 (Approved by University Grants Commission, India)

infinite output resistances M6 and M8 have equal currents and gate-source voltages i.e.

$$i_{D6} = i_{D8} = I_{bias} \tag{13}$$

$$v_{\text{GS6}} = v_{\text{GSB}} \tag{14}$$

It implies that the desired performance of the circuit is achieved when  $i_y=0$ . The drain currents  $i_{D7}$ ,  $i_{D9}$  are equal to the currents  $i_{D6}$  and  $i_{D8}$  when  $i_x=0$ . All drain currents of transistors in the translinear sections are equal to  $I_{bias}$ . Now when  $i_x\neq 0$ , then we can have

$$i_{D7} + i_X = i_{D9}$$

(15)

Since the complete current conveyor is symmetrical and all the CMOS transistors are matched then the following relationship holds for  $i_x \ll I_{bias}$

$$i_{D7} \approx I_{bias} - \frac{1}{2} i_X \tag{16}$$

$$i_{D9} \approx I_{bias} + \frac{1}{2}i_X \tag{17}$$

With the use of the mathematical equations stated above, the proposed circuit behaves as a current conveyor circuit by fulfilling all the required conditions with the best possible performance and can also be utilized in the realization of the various analog signal processing applications.

Fig. 5: Proposed Cascoded CMOS based CC-II circuit

## IV. SIMULATION RESULTS:

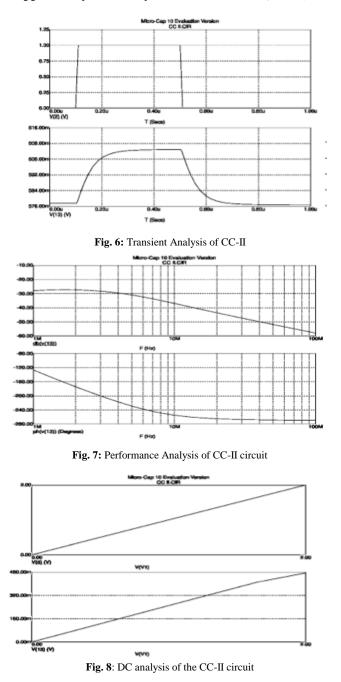

The 0.2µm CMOS technology has been used to simulate the proposed CC- II circuit for level 3 parameters. The proposed circuit performance has been discussed in this simulation on the basis of transient analysis, dc analysis of the current conveyor circuit and performance or noise analysis, with the use of modeled parameters. Fig: 6 show the transient analysis of the proposed circuit with the desired performance. It exhibits that according to the theoretical concepts, this circuit exactly replicate the input with the accepted level of delay and with a minimum possible deterioration of the desired signal. Fig: 7 show the performance analysis of the circuit with respect to the gain and the phase analysis to the desired limits. And the fig: 8 show the dc analysis of the circuit, with the input signal replication at the output of the system. The noise performance of the circuit was evaluated and the noise gain was found nearly zero. The proposed structure's power consumption increases marginally from its rated value.

#### V. CONCLUSION:

In this paper, the authors have presented the overview of an innovative high performance current conveyor circuit that is capable of operating at low voltages. The proposed CC-II in the paper is capable to be operated at 1.0 V and exhibits a power dissipation of 3mW having a bandwidth of 60 MHz. The range of the input current extends from -300 pA to 300 pA. This structure could be easily modified to function as CCI, CCII or CCIII. The various algorithms of the signal processing use mathematical functions which can be generated using the application of this circuit. This CMOS based cascoded CC-II circuit realizations forwards a circuit that provides a rail to rail swinging capability having excellent linearity. No compensating capacitors are required by the circuit so, they have a wide bandwidth which is independent of the gain. The given circuits operation is insensitive to the threshold voltage variation which is the result from the body effect. PSpice simulations which are based on the level-3 parameters obtained through CMOS are in total support with

### An Innovative Approach of High Performance CMOS Based Current Conveyor-II for ASP Applications

the expected results. The proposed CC-II circuit has better features and performance than the traditional ones.

# ACKNOWLEDGEMENT:

The authors are thankful to Mr. Aseem Chauhan (Additional President, RBEF and Chancellor AUR, Jaipur), Maj. General K. K. Ohri (AVSM, Retd.) Pro-VC, Amity University, Uttar Pradesh Lucknow, Wg. Cdr. A.K. Tiwari (Director ASET, Lucknow Campus), Brig. U. K. Chopra (Director AIIT & Dy. Director ASET), Prof O. P. Singh (HOD, Electrical & Electronics), Prof. H. K. Dwedi (Dy. Director, Research in Electronics) and Prof. N. Ram (Dy. Director ASET) for their motivation, kind cooperation, and suggestions.

#### **REFERENCES:**

- Rajinder Tiwari, R.K. Singh "An Innovative Approach of High Performance CMOS current conveyor - II for analog signal processing applications", IJCET Volume 3, Issue 1, January- June (2012), pp. 147-153.

- [2]. S. Kawada, Y. Hara, T. Isono, and T. Inuzuka, "1.5µm CMOS gate arrays with analog/digital macros designed using common base arrays," IEEE J. Solid-State Circuits, vol. 24, pp. 985–990, Aug. 1989.

- [3]. R. HogerVost, R. J. Wiegerink, P. A. L. de Jong, J. Fonderie, R. F. Wassenaar, and J. H. Huijsing, "CMOS low-voltage operational amplifiers with constant rail-to-rail input stage," in Proc. IEEE Int. Symp. Circuits Syst., May 1992, pp. 2876–2879.

- [4]. C. Toumazou, J. Lidgey, and A. Payne, "Emerging techniques for high frequency BJT amplifier design," in The First Int. Conf. Electron. Circuits Syst., Cairo, Egypt, Dec. 1994.

- [5]. B.Wilson, "Recent developments in current conveyors and current-mode circuits," Proc. Inst. Elect. Eng., vol. 137, pp. 63–77, Apr. 1990.

- [6]. A. Sedra and K. C. Smith, "A second generation current conveyor and its applications," IEEE Trans. Circuit Theory, vol. CT-17, pp. 132–134, Feb. 1970.

- [7]. M. C. H. Cheng and C. Toumazou, "3 V MOS current conveyor cell for VLSI technology," Electron. Lett., vol. 29, pp. 317–319, Feb. 1993.

- [8]. W. Surakampontorn, V. Riewruja, K. Kumwachara, and K. Dejhan, "Accurate CMOS based current conveyors," IEEE Trans. Instrum. Meas., vol. 40, pp. 699–702, Aug. 1991

- [9]. K. C. Smith and A. Sedra, "The Current Conveyor a New Circuit Building Block". Proc ZEEE... Proceedings Letters.. vol. 137. no. 2. pp. 1368-1369. August 1968.

- [10]. Oliaei. and J. Porte. "Conipound current conveyor". Electroil Lett.. vol. 33. no. 4. pp. 253 -254 13h Feb. 1997

- [11]. H. W. Cha. and K. Watanabe. "Wide band CMOS current conveyor". Electron Lett. vol. 32. no. 14. pp. 1245 -1246. 4h July 1996

- [12]. H. Elwan. and A. M. Soliman. "Low voltage. low power CMOS current conveyors". IEEE Trans. Circuits and Systems-I, vol. 44.110. 9. pp. 828-835. Sept. 1997

- [13]. S. S. Rajput. and S. S. Janiuar. "A high performance current mirror for low voltage designs". Proc. AFTCAS, Tianjin. China. Dec 7000

- [14]. S. S. Rajput and S. S. Jamuar. "Low voltage. low power high performance current mirror for portable analogue and mixed mode applications". accepted in IEE Proceedings. Circuits. Devices and Systems.

- [15]. S. 1. Liu. "Square rooting and vector summation circuits using current conveyors". ZEE Proc. Cimiits, Devices. Swteins. vol. 142. no. 4. pp. 223-226. Aug. 1995

- [16]. Sedra A., Robert G.: The current conveyor: history, progress and new results" IEE Proceedings Part G, 1990 137, pp: 78-87.

- [17]. E. Bruun, "A combined first- and second-generation current conveyor structure", Int. J. Electronics, Vol. 78, pp. 91 1-923, 1995.

- [18]. G. Di Cataldo, G. Palmisano, and G. Palumbo, "A CMOS CCII+", Proceedings of ISCAS 1995, 1995, Vol. 1, pp. 315-318

- [19]. E. Bruun, "Class AB CMOS first-generation current conveyor", Electronics Letters, Vol. 3 1, pp 422-423, March 1995.

- [20]. H. W. Cha, K. Watanabe. Wideband CMOS current conveyor. Electronics Letters. nr. 14; vol. 32; 1996; pp. 1245-1246.

- [21]. A. Fabre, M. Alami. A precise macromodel for second generation current conveyors. IEEE Transactions on Circuit and Systems-I. nr. 7; vol. 44; 1997; pp. 639-642.

[22]. X.Zhang, X.Ni, M.Iwahashi, N.Kambayashi. Realization of universal active complex filter using CCIIs and CFCCIIs. Analog Integrated Circuits and Signal Processing. nr. 20; 1999; pp. 129-137.

**Ayushi Chaurasia** was born in Varanasi (U.P.) India in 1993. She received her bachelor's degree of Engineering and Technology from United Institute of Technology from Allahabad (U.P.) India in 2015. She is currently working towards her M.Tech Degree in Electronics and Communication at Amity University, Lucknow. She is currently focused on her work on CMOS based Circuits using Cadence tools.

**Rajinder Tiwari** has received his Bachelor and Master degree in Electronics Science from University of Jammu, Jammu (J&K) in 1995 and 1998 respectively. He has received Master of Technology degree in Instrumentation Engineering from Department of Applied Sciences, National Institute of Technology, Kurukshetra (Formerly Regional

Engineering College, Kurukshetra) in 2002. He served Central Electronics Engineering Research Institute (CEERI), Pilani as Project Assistant in Hardware and Software Design for Integrated Tea Automation System Design from July, 2002 to July, 2005. He has joined Devcon Infrastructure Private Limited (DIPL), Mumbai as Sr. Software Engineer in Bridge Instrumentation Division i.e. Hardware & Software Design from Aug, 2005 to Jan, 2007. He has joined Department of Electrical & Electronics Engineering Amity University, Lucknow U.P. India as Lecturer in 2007, later, he has served in the capacity of Sr. Lecturer from Jul, 2010 to Jun, 2011 and Assistant Professor from Jul, 2011 to till dated. He has extensively published in several National & International Journals and Conferences of repute. He is associated with many International Journals as Reviewer with reputed publishers i.e. IEEE, IETE, SCOPUS, SCI Indexed Publications. He has delivered many Invited Lectures in the domain of Embedded System Design using LabVIEW & MatLAB. Mr Tiwari is a senior & lifetime member of IAEng, IETE, IET (U.K.), MRSI, & UACEEE. His areas of interest are Quantum Computing, Analog CMOS Circuits (VLSI), Embedded System Design & Industrial Automation System Design